### MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India)

Sponsored by CMR Educational Society

(Affiliated to JNTU, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC - "A" Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via Hakimpet), Secunderabad – 500100, Telangana State, India. Contact Number: 040-23792146/64634237, E-Mail ID: <u>mrcet2004@gmail.com</u>, website: <u>www.mrcet.ac.in</u>

## DEPARTMENT OF INFORMATION TECHNOLOGY II B.TECH I SEMESTER R17 SUPPLEMENTARY PREVIOUS QUESTION PAPERS

## LIST OF SUBJECTS

| CODE     | NAME OF THE SUBJECT                         |

|----------|---------------------------------------------|

| R17A0510 | Computer Organization                       |

| R17A0461 | Digital Logic Design                        |

| R17A0504 | Data Structures using C++                   |

| R17A0401 | Electronic Devices and Circuits             |

| R17A0503 | Mathematical Foundation of Computer Science |

| R17A0024 | Probability and Statistics                  |

#### Code No: **R17A0510** MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) **II B.Tech I Semester Supplementary Examinations, October 2020 Computer Organization** (CSE & IT) **Roll No** Time: 2 hours Max. Marks: 70 Answer Any Four Questions All Questions carries equal marks. \*\*\* 1 a) Represent the following decimal values as signed 7 bit number using sign magnitude, signed 1's complement and signed 2's complement formats: i)+43 iv)-27 ii) -10 iii)51 b) Explain the different registers that are available in the processor of a digital computer and the connection between the processor and the memory. a) What are the basic functional units present in the computer and explain 2 each of them? b) Design a 4 bit Arithmetic Circuit which can perform addition, subtraction, increment and decrement operations. a) Draw the flow chart for interrupt cycle and write in brief about modified 3 fetch phase. b) Define the following: i. Microoperation ii. Microinstruction iii. Microprogram iv. Microcode 4 a) What is instruction cycle? Explain various steps involved in the instruction cycle. b) Write the circuit of Microprogram sequencer for control memory, explain in brief. a) Explain the Stack Organization with example. 5 b) With a neat diagram explain floating point addition/subtraction unit. a) Discuss the differences between RISC and CISC. 6 b) Write Booth multiplier recoding table. Perform booth multiplication on the following numbers -13(multiplicand), +11 (multiplier). 7 a) Draw the block diagram of a DMA controller and explain its functioning. **b**) List the applications of Vector processing. Write in brief about vector operations. 8 a) List and explain different types of cache memory mapping techniques. **b**) How address mapped using pages in virtual memory? Explain. \*\*\*\*\*\*\*

### Code No: R17A0461 MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) II B.Tech I Semester Supplementary Examinations, October 2020

Digital Logic Design (IT)

\*\*\*

- 1 a) Represent the decimal number 6,248 in

- i) BCD

- ii) Excess-3 code

- iii) 2421 code

- iv) Hexadecimal

v) Octal

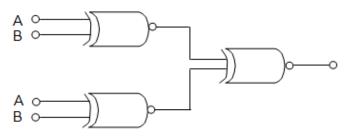

b) Find the output of the circuit shown in fig.

- **2** a) How can an AND-OR network be converted to all NAND network? Illustrate with an example.

- b) Implement the Boolean function: F = xy + x'y' + y'z

- (i) With AND, OR, and Inverter gates

- (ii) With OR and Inverter gates

- (iii) With AND and Inverter gates

- 3 a) Using the Karnaugh map method, simplify the following function; obtain its sum of the products form, and product of the sums form. Realize it with NAND gates:  $F(W, X, Y, Z) = \sum m(1, 3, 4, 5, 6, 7, 9, 12, 13)$

- b) Prepare a Karnaugh map for the following functions:

- i). F = A + B + C'

ii).

$$F = ABC + A'BC + B'C'$$

4 a) Using a Karnaugh map, simplify the following function and implement it with NOR gates

F (A, B, C, D) =  $\Pi$  M(2, 8, 11, 15) + d (3, 12, 14)

- b) Using the Quine-McCluskey method obtain all the prime implicants, essential prime implicants, and minimized Boolean expression for the function:

- $F(A, B, C, D, E) = \sum m (1, 3, 6, 10, 11, 12, 14, 15, 17, 19, 20, 22, 24, 29, 30)$

- 5 a) Design an 8-bit magnitude comparator using 4-bit comparators and other gates.

- b) How are multiplexers useful in developing combinational circuits?

- c) Show that the function  $f(w_1, w_2, w_3) = \sum m(1, 2, 3, 5, 6)$  can be implemented using a 3-to-8 binary decoder and an OR gate.

- 6 a) Construct a full-Subtractor using:

- (i) Basic gates,

- (ii) NAND gates, and

- (iii) NOR gates

- b) Realize  $16 \times 1$  Mux using only  $2 \times 1$  Mux.

- a) Design a 4-bit Johnson counter using D flip-flops and decoding gates.b) Design an 8-bit Ring counter.

- a) Design Dynamic RAM cell and then describe the read and write operation.b) Realize the system of functions by four-input ROM:

#### Code No: R17A0504 MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) II B.Tech I Semester Supplementary Examinations, October 2020 Data Structures using C++

Time: 2 hours

- Prepare a program to arrange the elements into sorting order using merge sort write various time complexity levels.

- 2 Write an algorithm to sort the elements using heap sort with an example and mention various time complexity levels.

- **3** Explain about Stack ADT and Queue ADT with examples.

- 4 How binary trees are represented? Explain about binary tree traversals with example.

- 5 Describe about priority queue using heaps. Illustrate insert and delete operations on priority queue.

- 6 In what way priority queues are useful. Prepare a model for external sorting and write multiway merge techniques with example.

- 7 Explain hashing. How it is useful?

Brief the following :

- i) Linear hashing ii) rehashing iii) extendible hashing

- 8 How do you represent AVL trees? Explain insertion, deletion and display operations on AVL trees.

\*\*\*\*\*\*\*

#### Code No: R17A0401 MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) II B.Tech I Semester Supplementary Examinations, October 2020 Electronic Devices and Circuits

(EEE, ECE, CSE & IT)

|         | <u></u> | _,_ |   | , -~ | <br>/ | - |   |   |      |           |

|---------|---------|-----|---|------|-------|---|---|---|------|-----------|

| Roll No |         |     |   |      |       |   |   |   |      |           |

|         | •       |     | - |      |       |   | - | N | Лах. | Marks: 70 |

Time: 2 hours

All Questions carries equal marks.

\*\*\*\*

- 1 (a) Draw and explain the VI characteristics of a PN Junction diode. Also explain the effect of temperature on these characteristics.

- (b) Derive the equation for the Transition capacitance of a PN junction diode.

- 2 (a) Explain in detail about Zener breakdown and Avalanche multiplication.

- (b) Explain in detail about (i) Varactor diode and (ii) photo diode

- 3 (a) Draw the circuit diagram of a Bridge rectifier and explain its operation with the help of input and output waveforms.A sinusoidal voltage of amplitude 15V and frequency 50 Hz is applied to a half-

- (b) wave rectifier. Given that  $RL = 1K\Omega$ ,  $R_f = 10\Omega$  and  $Rr = \infty$ . Find (i) Peak, Average and RMS values of current (ii) DC output power (iii) AC input power (iv) Efficiency and (v) Ripple factor.

- 4 (a) Compare Half wave, Full wave and Bridge rectifiers.

- (b) Draw the diagram of Centre-tapped full wave rectifier with Inductor filter and explain its operation. Also derive the equation for ripple factor.

- (c) Explain how the Zener diode acts as a Voltage regulator?

- 5 (a) Explain various current components in an *npn* Transistor. Derive the relation between  $\alpha$  and  $\beta$ .

- (b) Draw and explain the input and output characteristics of BJT in common-emitter configuration. Also explain the effect of base width modulation on these characteristics.

- 6 (a) Draw the *h*-parameter model of transistor in CB configuration and derive the expressions for Voltage gain, current gain, input impedance and output impedance.

- (b) Given that  $h_{fe} = 50$  and  $h_{ie} = 0.8 \text{K}\Omega$ . Find the values of  $h_{fb}$  and  $h_{ib}$ .

- 7 (a) Derive the expressions for three stability factors for a fixed bias circuit.

- (b) Explain in detail about Thermistor and Sensistor Compensation techniques.

- 8 (a) How FET can be used as a Voltage variable resistor? Explain.

- (b) Explain the constructional details of enhancement type MOSFET. Also explain the drain and transfer characteristics.

\*\*\*\*\*\*\*

### Code No: R17A0503 MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) II B.Tech I Semester Supplementary Examinations, October 2020

Mathematical Foundation of Computer Science

|         | ( | SE | ÅΓ | <b>I</b> ) |  |  |  |

|---------|---|----|----|------------|--|--|--|

| Roll No |   |    |    |            |  |  |  |

Time: 2 hours

1

Max. Marks: 70

R17

Answer Any **Four** Questions All Questions carries equal marks.

- a) Show that  $\neg P \land (\neg Q \land R) \lor (Q \land R) \lor (P \land R) \Leftrightarrow R$  without constructing truth table

- b) write the equivalence formulas of predicate statements and find the negation of the statement  $\left[ \forall x \exists y \left[ \left( p(x, y) \land q(x, y) \right) \rightarrow r(x, y) \right] \right]$

- 2 a) Prove the equivalence  $p \lor q \lor (\neg p \land \neg q \land r) \Leftrightarrow p \lor q \lor r$

- b) Show that  $R \lor S$  follows logically from the premises  $C \lor D$ ,  $(C \lor D) \to \neg H$ ,  $\neg H \to (A \land \neg B)$  and  $(A \land \neg B) \to (R \lor S)$ .

- 3 a) Let  $A = \{1, 2, 3, 4\}$ . Give an example of a relation on A that is:

i)Reflexive & Symmetric but not Transitiveii) Reflexive & Transitive, but not Symmetriciii) Symmetric & Transitive but not Reflexiveiv)Equivalence relationv) Only antisymmetric

- b) Give the converse and contra positive of the implication of the statement "If it is raining then I get wet".

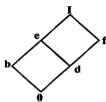

- a) Define the bounded lattice, consider the bounded lattice L in the following figure

- i) Find the complements of each element in the figure(if exist)

- ii) Is L distributive? Justify your answer

b)  $R: A \to A$ ,  $A = \{1, 2, 3, 4\}, R = \{(1, 4), (2, 3), (4, 2), (3, 3), (1, 1)\}$  find the transitive closure of the relation?

a) A group of 8 is composed of 5 psychologists and 3 sociologists.

4

5

i) In how many ways can a committee of 5 be formed?

ii) In how many ways can a committee of 5 be formed that has 3 psychologists and 2 sociologists?

- b) How many different ways a 5 digit number (n) can be prepared using digits  $\{0, 1, 2, 5, 6\}$ , where n >5000.

- **6** Show that

- i)  $nC_0 + nC_1 + nC_2 + \dots + nC_n = 2^n$

- ii)  $nC_0 nC_1 + nC_2 + \dots + (-1)^n nC_n = 0$

- iii) Give the 3 combinations of {3.a,2.b,2.c,1.d}

- 7

- a) Solve the recurrence relation of  $a_n+5a_{n-1}+6a_{n-2}=0$

- b) Solve the recurrence relation using generating functions  $a_n-6a_{n-1}+12a_{n-2}-8a_{n-3}=0$  where  $n\geq 3$

- 8

- a) How many vertices will the following graphs have, if they contain

- i) 16 edges and all vertices of degree 4?

- ii) 21 edges, 3 vertices of degree 4, and other vertices of degree 3

- iii) 11 edges,6 vertices of degree3, and other vertices of degree less than 3

- b) Find the below graph is planar or not

#### Code No: R17A0024 MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India)

II B.Tech I Semester Supplementary Examinations, October 2020 Probability and Statistics

| •    |                   |  |

|------|-------------------|--|

| (CSE | <b>&amp; IT</b> ) |  |

|         |  | ~ 1 | <u> </u> |  |     |     |

|---------|--|-----|----------|--|-----|-----|

| Roll No |  |     |          |  |     |     |

|         |  |     |          |  |     |     |

|         |  |     |          |  | 3.6 | 3.6 |

Time: 2 hours

Max. Marks: 70

# Answer Any **Four** Questions All Questions carries equal marks.

\*\*\*\*

- **1a** Define probability Mass and Density function.

- **b** A random variable X has the following probability function :

| x         | 0       | 1        | 2  | 3    | 4  | 5                     | 6      | 7          |

|-----------|---------|----------|----|------|----|-----------------------|--------|------------|

| P(x)      | 0       | K        | 2K | 2K   | 3K | <i>K</i> <sup>2</sup> | $6K^2$ | $7K^2 + K$ |

| Determine | i) K ii | ) Evalua |    | <5). |    |                       |        |            |

2a The probability density of a random variable is given by

$f(x) = \begin{cases} k(1-x^2), for \ 0 < x < 1\\ 0, otherwise \end{cases}$  find the value of 'K'

- **b** In a normal distribution, 7% of the items are under 35 and 89% of the items are under 63. Determine the mean and variance of the distribution.

- **3a** If the two lines of regression are y = 0.8x + 1.2 and x = 0.4y + 1, then find the means of x and y.

- **b** A random of 5 college students is selected and their marks in mathematics and Statistics are found to be

| Mathematics | 85 | 60 | 73 | 40 | 90 |

|-------------|----|----|----|----|----|

| Statistics  | 93 | 75 | 65 | 50 | 80 |

Calculate rank correlation coefficient.

4 For the following data ,find equations of the two regression lines

| Х | 1  | 2  | 3  | 4  | 5  |

|---|----|----|----|----|----|

| Y | 15 | 25 | 35 | 45 | 55 |

- **5a** Define Null hypothesis and Alternate Hypothesis

- **b** The means of two large samples of sizes 1000 and 2000 members are 67.5 inches and 68 inches respectively. Can the samples be regarded as drawn from the same population of S.D 2.5 inches

- 6a Define Type-I and Type-II errors

- **b** In a sample of a 1000 students 500 uses ball pen and in another sample of 3500 students 1400 use ball pens. Test the significance between the difference of two proportions at 5% level

- 7a Write the properties of t-distribution.

- **b** Two horses 'A' and 'B' were tested according to the time( in seconds) to run a particular track with the following results:

| Horse 'A' | 28 | 30 | 32 | 33 | 33 | 29 | 34 |

|-----------|----|----|----|----|----|----|----|

| Horse 'B' | 29 | 30 | 30 | 24 | 27 | 29 |    |

Test whether the two horses have the same running capacity. ('t' Table value= 2.2)

- 8a Define i) Balking ii) Reneging in Queuing System

- **b** A T.V repair man finds that the time spent on his jobs has an exponential distribution with mean 30 minutes. He repairs sets in the order which they arrive. The arrival of the sets is approximately poisson with an average of 10 per an eight hour day. Find the repairman's idle time each day.

\*\*\*\*\*\*